बोल्ट ग्राफिक्स ने अपने ज़ीउस जीपीयू के लिए टेस्ट चिप को टेप-आउट कर दिया है जिसका लक्ष्य एचपीसी की लागत में कटौती करना और वर्कलोड को 17 गुना तक कम करना है। वॉल्यूम उत्पादन Q4 2027 के लिए निर्धारित है।

बोल्ट कहते हैं, कंपनियों ने लागत दक्षता के बजाय चरम प्रदर्शन के लिए कंप्यूट आर्किटेक्चर को अनुकूलित किया है, जिससे बुनियादी ढांचे की लागत एक प्राथमिक बाधा बन गई है।

चूंकि अधिकांश कार्यभार इन आर्किटेक्चर पर निर्भर रहता है, इसलिए उपलब्ध बाजार का बड़ा हिस्सा आर्थिक रूप से अलाभकारी बना हुआ है।

बोल्ट के संस्थापक, सीईओ और सीटीओ दरवेश सिंह कहते हैं, “कंप्यूटर की मांग तेजी से बढ़ रही है, लेकिन लागत एक सीमित कारक बनी हुई है।”

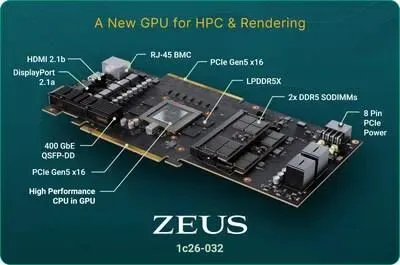

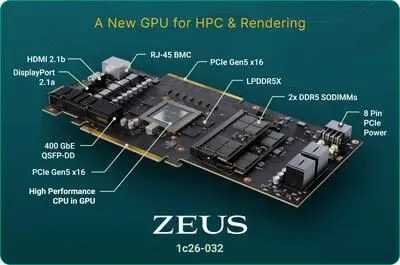

ज़ीउस प्लेटफ़ॉर्म एक कस्टम जीपीयू आर्किटेक्चर को एक पूर्ण सॉफ़्टवेयर स्टैक के साथ एकीकृत करता है ताकि कई कंप्यूट बाज़ारों में संचालित करने के लिए डिज़ाइन किया गया एक एकीकृत सिस्टम बनाया जा सके।

प्लेटफ़ॉर्म स्थापित सेमीकंडक्टर प्रक्रियाओं का उपयोग करता है, परीक्षण चिप को TSMC 12 FFC में सफलतापूर्वक डिज़ाइन किया गया है। ज़ीउस स्केलेबल आर्किटेक्चर 5 एनएम सहित उन्नत नोड्स को भी संबोधित करता है।

ज़ीउस शुरू में एचपीसी और रेंडरिंग वर्कलोड को लक्षित करेगा जिसमें $55 बिलियन+ टीएएम है और जहां 90% से अधिक गणना अभी भी सीपीयू पर चलती है और फिर गेमिंग और एआई वर्कलोड में विस्तार करेगी।