इस प्रकार, एडीसी एआई- और क्लाउड-संचालित डेटासेंटरों की तेजी से बढ़ती थ्रूपुट और प्रसंस्करण मांगों को पूरा करता है, बिना क्षेत्र और बिजली विस्फोट के, जो आमतौर पर अल्ट्रा-हाई सैंपलिंग दरों पर देखा जाता है।

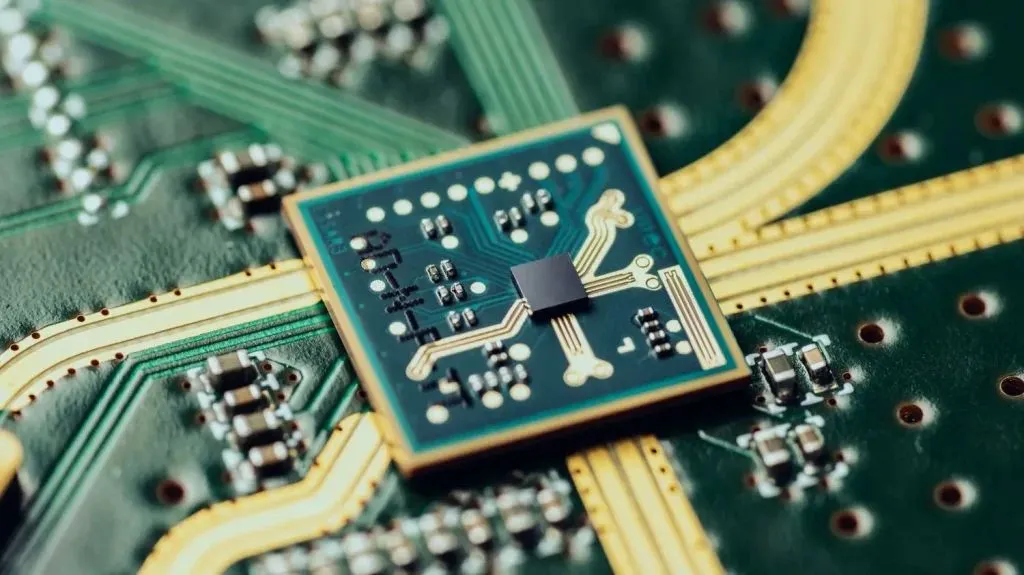

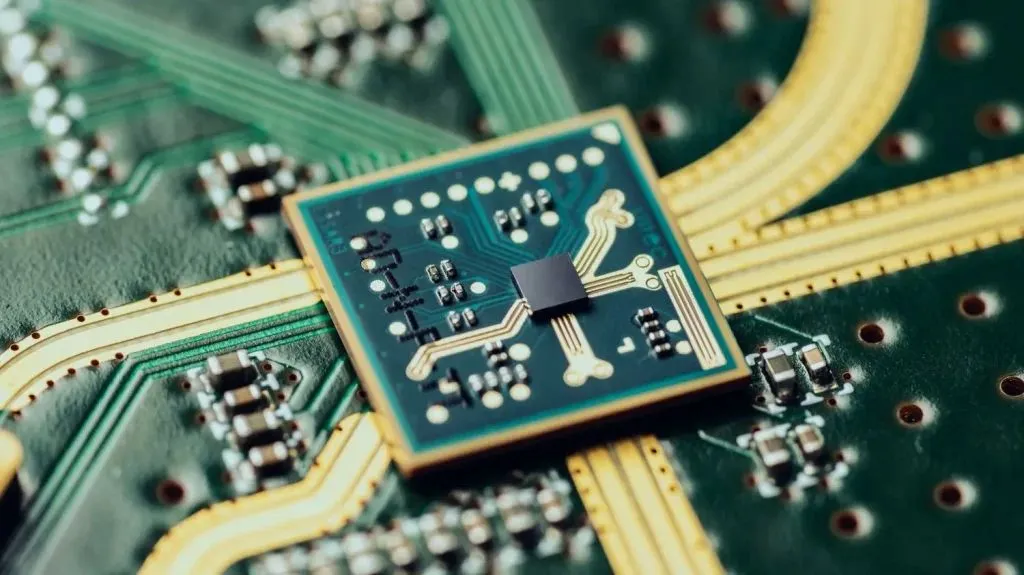

एआई और क्लाउड अनुप्रयोगों द्वारा संचालित, डेटा केंद्रों के ऑप्टिकल संचार नेटवर्क को उच्चतर थ्रूपुट और प्रसंस्करण मांगों को संभालने के लिए निरंतर उन्नयन की आवश्यकता होती है।

लेकिन जैसे-जैसे नमूना दर 100जीएस/एस से आगे बढ़ती है, अंतर्निहित घटक – जैसे वायरलाइन एडीसी, ऑप्टिकल ट्रांससीवर्स में आवश्यक – आकार में बढ़ने लगते हैं, लंबे इंटरकनेक्ट की आवश्यकता होती है, और परजीवी और ऊर्जा हानि शुरू होती है।

2024 आईएसएससीसी में, आईएमसी ने इस चुनौती का बड़ी सफलता से सामना किया: बड़े पैमाने पर टाइम-इंटरलीव्ड स्लोप-एडीसी आर्किटेक्चर पारंपरिक डिजाइनों से कम से कम दोगुना कॉम्पैक्ट और अत्याधुनिक बिजली दक्षता की विशेषता वाला है।.

उस दृष्टिकोण पर निर्माण करते हुए, imec अब एक रिकॉर्ड-छोटे एडीसी की शुरूआत के साथ अगला कदम उठा रहा है जो अल्ट्रा-हाई सैंपलिंग दरों पर सटीक सिग्नल रूपांतरण और विस्तृत बैंडविड्थ सुनिश्चित करता है।

“हमारा 7-बिट, 175GS/s ADC – 5nm FinFET तकनीक में कार्यान्वित – 250 x 250μm2 के रिकॉर्ड-छोटे कोर क्षेत्र और कम रूपांतरण ऊर्जा (प्रति नमूना 2.2 pJ) को जोड़ता है, एक नमूना गति के साथ जो अब तक की सबसे तेज़ रिपोर्ट में से एक है। यह इसे डिजिटल-सघन वायरलाइन इंटरकनेक्ट्स को बढ़ाने के लिए एक आकर्षक समाधान बनाता है, जहां हर वर्ग माइक्रोन और मिलीवाट की गिनती होती है,” कहते हैं इमेक के पीटर ओसियूर।

दो पेटेंटयुक्त नवाचार इसे संभव बनाते हैं। सबसे पहले, एक नया रैखिककरण दृष्टिकोण – ढलान संकेत को आकार देना – विकृतियों को ठीक करता है। दूसरा, स्विच किए गए इनपुट बफ़र्स एडीसी के 2,048-चैनल टाइम-इंटरलीव्ड ऐरे को कुशलतापूर्वक फीड करते हैं, विद्युत भार को कम करते हैं और सिग्नल अखंडता से समझौता किए बिना अल्ट्रा-फास्ट सैंपलिंग को सक्षम करते हैं।

इस साल के आईएसएससीसी में प्रस्तुत एडीसी पर निर्माण करते हुए, आईएमसी अब 3एनएम फॉलो-ऑन डिजाइन विकसित कर रहा है और 14 एंगस्ट्रॉम डिजाइनों की खोज कर रहा है, यह पता लगा रहा है कि उच्च प्रदर्शन वाले वायरलाइन डेटा कनवर्टर डिजाइनों के लिए ऐसे उन्नत नोड्स का लाभ कैसे उठाया जा सकता है।

पीटर ओसिउर: “आईएमईसी के पास संचार अनुप्रयोगों के लिए उच्च गति वाले एकीकृत सर्किट विकसित करने का एक लंबा ट्रैक रिकॉर्ड है। हमारे प्रमुख अनुसंधान ट्रैक में से एक ऑप्टिकल ट्रांससीवर्स (और उनके बिल्डिंग ब्लॉक्स) पर केंद्रित है जो वायरलाइन सिस्टम में तेजी से बढ़ती डेटा दरों के साथ तालमेल रख सकते हैं। इस संदर्भ में, हमारे एडीसी भविष्य के वायरलाइन अनुप्रयोगों के लिए कॉम्पैक्ट, कम-शक्ति कनवर्टर्स की एक नई पीढ़ी की दिशा में एक महत्वपूर्ण कदम का प्रतिनिधित्व करते हैं, जो अल्ट्रा-हाई स्पीड पर एसएआर-आधारित एडीसी आर्किटेक्चर की प्रदर्शन सीमाओं से आगे बढ़ते हैं। इसे तेज करने के लिए प्रयास, हम साझेदारों को गर्मजोशी से आमंत्रित करते हैं – जिसमें वायरलाइन कनेक्टिविटी बिल्डिंग ब्लॉक विकसित करने वाली फैबलेस कंपनियां भी शामिल हैं – हमारे एडीसी और डीएसी अनुसंधान कार्यक्रमों में शामिल होने के लिए, आईएमसी के अंतर्निहित आईपी पोर्टफोलियो तक पहुंचने के लिए लाइसेंसिंग विकल्प उपलब्ध हैं।

हमारी सभी Imec सामग्री देखें।