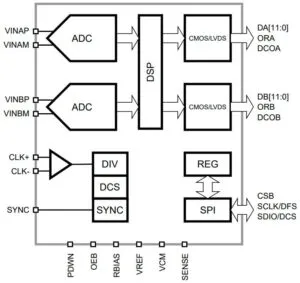

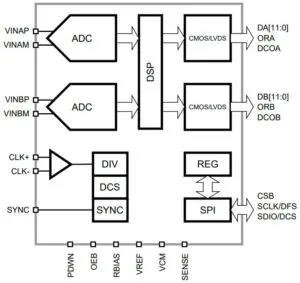

कंपनी के अनुसार, “डीएसपी का एकीकरण कई कार्यों को ऑन-चिप लाता है, जिसमें डिकिमेशन, डिजिटल डाउन-कनवर्जन, इंटरलीविंग और आईक्यू-बेमेल सुधार शामिल हैं – इन्हें पारंपरिक रूप से एफपीजीए द्वारा किया जाएगा।”

दोहरे चैनल, 12 बिट, 170Msample/s ADC संस्करण को SD1146 कहा जाता है।

सिलन्ना ने दावा किया, “डिवाइस व्यापक इनपुट सिग्नल बैंडविड्थ पर उच्च सिग्नल-टू-शोर अनुपात और रैखिकता प्राप्त करने के लिए मल्टीस्टेज पाइपलाइन आर्किटेक्चर का उपयोग करता है।”

सरलीकृत डीएसपी ब्लॉक आरेख

इसमें 70.8dBfs के दावा किए गए सिग्नल-टू-शोर, 88dBc SFDR (नकली मुक्त गतिशील रेंज), और -151.3dBfs/Hz इनपुट-शोर के साथ 2Vp-p नाममात्र इनपुट है – सभी इनपुट पर 70.2MHz के साथ, 170Msample/s पर नमूनाकरण। (यहां ‘एफएस’ ‘पूर्ण-पैमाने’ है)।

एडीसी को व्यक्तिगत रूप से, या एक ही सिग्नल के लिए I और Q चैनल के रूप में संचालित किया जा सकता है।

उनके सामने के सिरों पर एक नमूना-और-पकड़ है और शोर अस्वीकृति के लिए पूरी तरह से भिन्न है।

सिलन्ना ने कहा, “इनपुट चरण एक स्विच्ड-कैपेसिटर नेटवर्क के रूप में व्यवहार करता है, जो खुद को स्विच और सैंपलिंग कैपेसिटर के संयोजन के रूप में ड्राइविंग सर्किट में प्रस्तुत करता है।” “प्रत्येक रूपांतरण चक्र से पहले कैपेसिटर को रीसेट किया जाता है, जो आमतौर पर कुछ पाइपलाइन एडीसी आर्किटेक्चर में देखे जाने वाले गैर-रेखीय मेमोरी प्रभावों को प्रभावी ढंग से समाप्त कर देता है।”

कैपेसिटर के माध्यम से इनपुट को एसी-युग्मित किए जाने की उम्मीद है, और एक वोल्टेज आउटपुट प्रदान किया जाता है जिसके साथ इनपुट डीसी मान सेट किया जा सकता है। रूपांतरण के लिए एक आंतरिक 1.02 – 1.07V संदर्भ शामिल है।

स्विच-ऑन पर अंशांकन स्वचालित है, और ऑपरेशन के दौरान मैन्युअल रूप से शुरू किया जा सकता है। इसमें बैकग्राउंड कैलिब्रेशन मोड भी है।

नियंत्रण एक तीन-तार एसपीआई-संगत बस के माध्यम से होता है और आईसी को अपने डेटा आउटपुट को सीएमओएस या एलवीडीएस (एएनएसआई-644) स्तरों पर और ऑफसेट बाइनरी, टूएस पूरक या ग्रे कोड प्रारूप में संचालित करने के लिए सेट किया जा सकता है।

1GHz तक की बाहरी घड़ी की आवश्यकता होती है, या तो अंतर या एकल-समाप्त रूप में। इसे 1 से 8 के अभिन्न अनुपात वाले आंतरिक विभाजक द्वारा संसाधित किया जाता है।

1.8V एनालॉग और डिजिटल आपूर्ति की आवश्यकता है, और बिजली की खपत आमतौर पर 170Msample/s पर 492.4mW है। ऑपरेशन -40 से +85°C से अधिक है।

14 और 16 बिट एडीसी संस्करण विकासाधीन हैं, जिनकी नमूना दर 5 से 250 एमसैंपल/एस है।

खोजें इस सिलन्ना वेब पेज पर SD1146 डेटा शीटऔर यहां कंपनी के पहले के डीएसपी-कम एडीसी के बारे में जानें